Here I will constantly some of the projects I have been working on and the corresponding description of the projects. Currently, my interest mainly lies in the field Distributed System and Machine Learning. I am a participant for various super computing competition and I am thrilled to apply the power of supercomputer into solving some of the Machine Learning problems.

CS109 Jungle Java

Contributors:

- Mengxuan Wu

- Yicheng Xiao

The project of CS109 aims at creating an interactive Jungle. During the project, we have realized the basic function, the AI module (Mengxuan Wu has implemented the hard AI with Monte Carlo Tree Search, Yicheng Xiao has implemented the medium AI with min-max algorithms with alpha-beta pruning). Mengxuan Wu has further realized the multiplayer modes. Yicheng Xiao is responsible for the GUI.

CS211 Electronic Organ Verilog

Contributors:

- Mengxuan Wu

- Shengli Zhou

- Yicheng Xiao

It is asked to implemented a Electronic Organ using FPGA board with verilog. Mengxuan Wu accounts for the memory module. Shengli Zhou accounts for input module and the state machine of the whole game. Yicheng Xiao accounts for Buzzer and VGA modules.

In the project, the Buzzer can support from C3 to C5 and can produce multiple notes at the same time. The VGA has been realized to top up the engagement of the game.

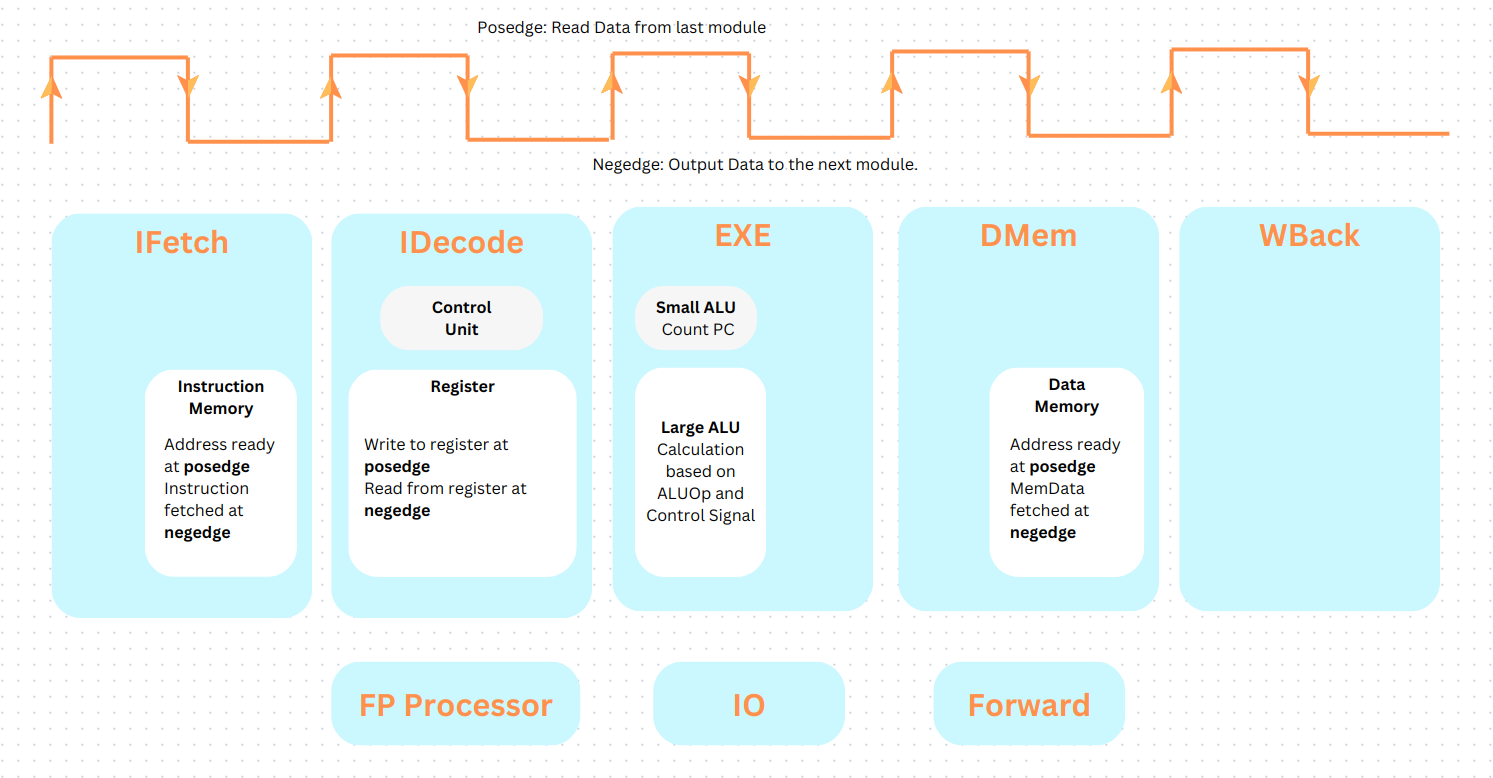

CS214 Pipelined CPU Verilog

Contributors:

- Yicheng Xiao

- Shengli Zhou

- Haibin Lai

We have designed a pipelined RISC-V CPU with the following structure:

We have realized the following instructions:

| Instruction | Encoding | Data Flow | Usage |

|---|---|---|---|

| R-Type Instruction | Opcode: 0110011 | ||

| add | funct7: 0x00 funct3: 0x0 | Register(rs1, rs2) -> ALU -> WB -> Register(rd) | add rd, rs1, rs2 |

| xor | funct7: 0x00 funct3: 0x4 | Register(rs1, rs2) -> ALU -> WB -> Register(rd) | xor rd, rs1, rs2 |

| and | funct7: 0x00 funct3: 0x7 | Register(rs1, rs2) -> ALU -> WB -> Register(rd) | and rd, rs1, rs2 |

| I-Type-Immediate Instruction | Opcode: 0010011 | ||

| addi | funct3: 0x0 | Register(rs1) \ ID(Imm) -> ALU -> WB -> Register(rd) | addi rd, rs1, Imm |

| xori | funct3: 0x4 | Register(rs1) \ ID(Imm) -> ALU -> WB -> Register(rd) | xori rd, rs1, Imm |

| andi | funct3: 0x7 | Register(rs1) \ ID(Imm) -> ALU -> WB -> Register(rd) | andi rd, rs1, Imm |

| slli | funct3: 0x1 | Register(rs1) \ ID(Imm) -> ALU -> WB -> Register(rd) | slli rd, rs1, Imm |

| srli | funct3: 0x5 | Register(rs1) \ ID(Imm) -> ALU -> WB -> Register(rd) | srli rd, rs1, Imm |

| I-Type-Load Instruction | Opcode: 0000011 | ||

| lb | funct3: 0x0 | Register(rs1) \ ID(Imm) -> ALU -> DMem -> WB -> Register(rd) | lb rd, Imm(rs1) |

| lbu | funct3: 0x4 | Register(rs1) \ ID(Imm) -> ALU -> DMem -> WB -> Register(rd) | lbu rd, Imm(rs1) |

| lw | funct3: 0x2 | Register(rs1) \ ID(Imm) -> ALU -> DMem -> WB -> Register(rd) | lw rd, Imm(rs1) |

| I-Type-Jump Instruction | Opcode: 1100111 | ||

| jalr | funct3: 0x0 | 1. Register(rs1) \ ID(Imm) -> ALU -> IF | jalr rd, Imm(rs1) |

| 2. IF(PC) -> ID -> ALU -> WB -> Register(rd) | |||

| I-Type-Ecall Instruction | Opcode: 1110011 | ||

| S-Type Instruction | Opcode:0100011 | ||

| sw | funct3: 0x2 | Register(rs1) \ ID(Imm) -> ALU -> DMem(Mem[rs1 + Imm] = rs2) | sw rs2, Imm(rs1) |

| B-Type Instruction | Opcode: 1100011 | ||

| beq | funct3: 0x0 | Register(rs1, rs2) -> ALU -> IF | beq rs1, rs2, Label |

| bne | funct3: 0x1 | Register(rs1, rs2) -> ALU -> IF | bne rs1, rs2, Label |

| blt | funct3: 0x4 | Register(rs1, rs2) -> ALU -> IF | blt rs1, rs2, Label |

| bge | funct3: 0x5 | Register(rs1, rs2) -> ALU -> IF | bge rs1, rs2, Label |

| bltu | funct3: 0x6 | Register(rs1, rs2) -> ALU -> IF | bltu rs1, rs2, Label |

| bgeu | funct3: 0x7 | Register(rs1, rs2) -> ALU -> IF | bgeu rs1, rs2, Label |

| J-Type Instruction | Opcode: 1101111 | ||

| jal | ID(Imm) -> ALU -> PC \ ID(PC) -> ALU -> WB -> Register(rd) | jal rd, Label | |

| U-Type Instruction | Opcode: 0110111 | ||

| lui | ID(Imm) -> ALU -> WB -> Register(rd) | lui rd, Imm |

CS305 Reliable Data Transfer Python

Contributors:

- Yujun He

- Zhaoyang Hong

- Yicheng Xiao

For the socket package, we can only use the method for UDP, which is recvfrom() and sendto().

We need to use threads to maintain a “connection” between the client and the server, because the server needs to be able to handle multiple clients at once.

Each socket is binded to an address and a port, while connecting to a server, the client needs to know the address and the port of the server.

After the server gets the address and the port of the client, it will maintain a FSM with the according client to form a “connection”.

SWS3004 GroupUp React

Contributors:

- Zhengdong Huang, Backend Design and Cloud Service Design

- Hemu Liu, Backend Design and Cloud Service Design

- Zihang Wu, Frontend Design

- Yicheng Xiao, Frontend Design and Recommender Service Design

When our class begins, we are required to find our teammates. It is not uncommon that we tend to naturally group up with someone from the same universities because of familiarity. However, by grouping up like this, we cannot even get to know each other pretty well. Then this idea comes across us: We can design a cloud-based grouping application for this scenario! We aim to design a system where you can find your teammates based on recommendation!

CS323 Incredibuild Rust

Contributors:

- Ben Chen

- Yicheng Xiao

- Jiarun Zhu

SPL(SUSTech Programming Language) Compiler in Rust. Current implementation mainly focuses on Compiler frontend, including Lexer, Parser, AST, Type Checker and LLVM IR generation. The backend we use is LLVM. The grammar supported is as follows:

1 | // Program Structure |

Based on the tools we use Logos and lalrpop, we have realized self-defined error-recovery mechanism that can detect lexical errors and syntax errors. In the analyzer module, we have conducted type checking and semantic analysis. As the last step, we use inkwell to generate LLVM IR code.

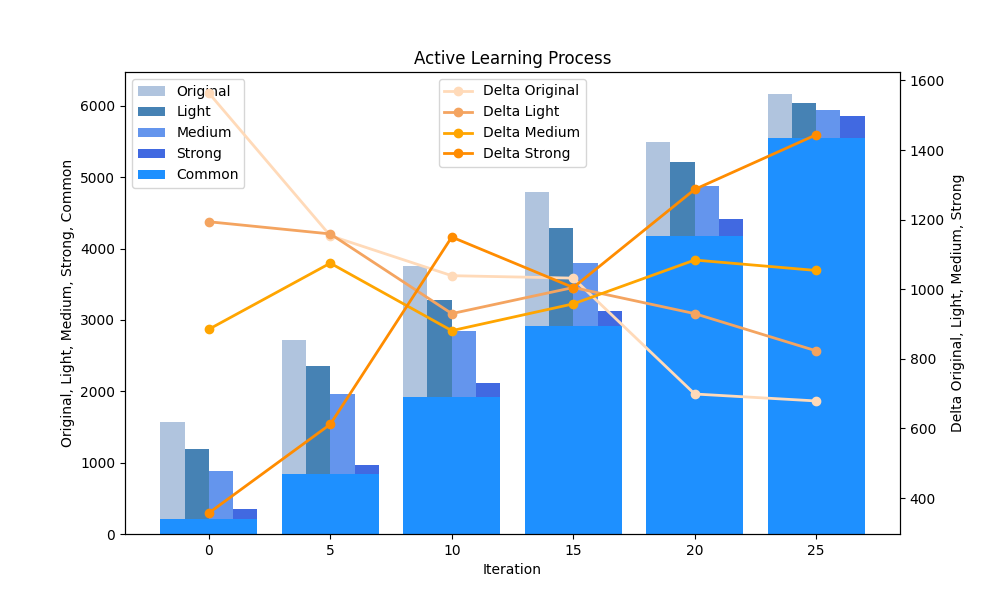

CS329 When AL and DA meets at OD Python

The full name stands for “When Active Learning and Data Augmentation meets at Object Detection”.

Contributors:

- Shengli Zhou

- Yicheng Xiao

In this project, we studied the effect of Active Learning and Data Augmentation on Object Detection. We use infromation entropy and information gain as the criterion for Active Learning. Also, we chose different levels of Data Augmentation techniques. We used RTDETR-v2 as our pre-trained model and train it on the Kitti 3D Object Detection 2017 dataset. Through our finetuning process, we observed a correlation between the selection strategy and the according data augmentation strategy that can probably give us better understanding of the learning process and guide us what data should we choose to improve the performance. Check out the report here!

CS334 VirtIO for crypto device on Asterinas Rust

Contributors:

- Jiarun Zhu

- Shengli Zhou

- Yicheng Xiao

This is a simple implementation of a VirtIO crypto device. The device is a PCI device that can be used to encrypt and decrypt data. The device is implemented in QEMU. Check out the report here!

We have implemented the following features:

- [x] Symmetric Algorithm

- [x] Cipher (Encrypt/Decrypt)

- [x] Chain Algorithm

- [x] Hash Algorithm (Encrypt/Decrypt)

- [ ] MAC Algorithm (Encrypt/Decrypt)

- [x] AKCIPHER Algorithm (Encrypt/Decrypt/Sign/Verify)

- [x] Writing Test Cases

- [x] Asynchronous Request

- [x] User Call

CS304 PeachIDE TypeScript

Contributors:

- Ben Chen

- Mingzhi Chen

- Tianrun Qiu (PM)

- Yicheng Xiao

- Zhuo Wang

PeachIDE is an Intelligent Course-Aware IDE designed to integrate coding with learning resources. The project aims to transform how students engage with programming courses by making lectures more interactive, learning more intuitive, and collaboration seamless.

Key Features:

- Intuitive Course Resource Management: Provides a structured interface for organizing course materials. Users can take digital notes directly within the IDE, bookmark key concepts, and link resources to coding exercises for easy reference.

- Code-Linked Lecture Execution: Lecture slides are embedded within the IDE, allowing students to modify and execute code snippets inline. This feature enables real-time experimentation with lecture examples and immediate feedback on code correctness.

- Collaborative Coding & Resource Sharing: Supports real-time collaborative coding, discussion threads linked to lecture content, resource sharing among students, and built-in chat for team projects.

- Course Progress Tracking: Tracks student progress through the course materials, showing completed tasks, upcoming assignments, and contents needing attention.

- AI Learning Assistant: Summarizes lecture content, highlights key takeaways, generates mind map or flow charts for visualization, and creates quizzes for self-assessment with auto-grading and explanations.

The project is built using TypeScript (77.2%), Python (18.9%), JavaScript (2.3%), and CSS (1.2%), providing a modern, full-stack solution for educational programming environments.

Academic Record SUSTech

| Course Code | Course Name | Semester | Instructor | Final Grade |

|---|---|---|---|---|

| MA117 | Calculus I | 2022 Fall | Rong Wang | 99 |

| MA127 | Calculus II | 2023 Spring | Rong Wang | 99 |

| MA113 | Linear Algebra | 2022 Fall | Yimao Chen | 97 |

| CS104 | Introduction to Mathematical Logic | 2023 Spring | Mingxin He | 100 |

| CS109 | Introduction to Computer Programming | 2023 Spring | Jianqiao Yu | 98 |

| CS211 | Digital Logic (H) | 2023 Fall | Yuhui Bai | 97 |

| CS213 | Principles of Database Systems (H) | 2023 Fall | Shiqi Yu | 96 |

| CS214 | Computer Organization (H) | 2024 Spring | Yuhui Bai | 97 |

| CS215 | Discrete Matrhematics (H) | 2023 Fall | Qi Wang | 86 |

| CS216 | Algorithm Design and Analysis (H) | 2024 Spring | Shan Chen | 91 |

| CS217 | Data Structures and Algorithms Analysis (H) | 2023 Fall | Pietro Simone Oliveto | 97 |

| CS305 | Computer Networks | 2024 Spring | Zhuozhao Li | 92 |

| CS311 | Artificial Intelligence (H) | 2024 Spring | Bo Yuan | 83 |

| CS323 | Compiler | 2024 Fall | Yepang Liu | 95 |

| CS329 | Machine Learning | 2024 Fall | Qi Hao | 97 |

| CS334 | Operating System | 2024 Fall | Yiqian Zhang | 98 |

| MA212 | Probability and Statistics | 2023 Fall | Yiwei Zhang | 95 |